국내 연구진이 `0`과 `1`로 표현되는 기존 2진법 디지털 방식이 아닌 `0·1·2`인 3진법으로 구현되는 반도체를 세계 최초로 선보였다.

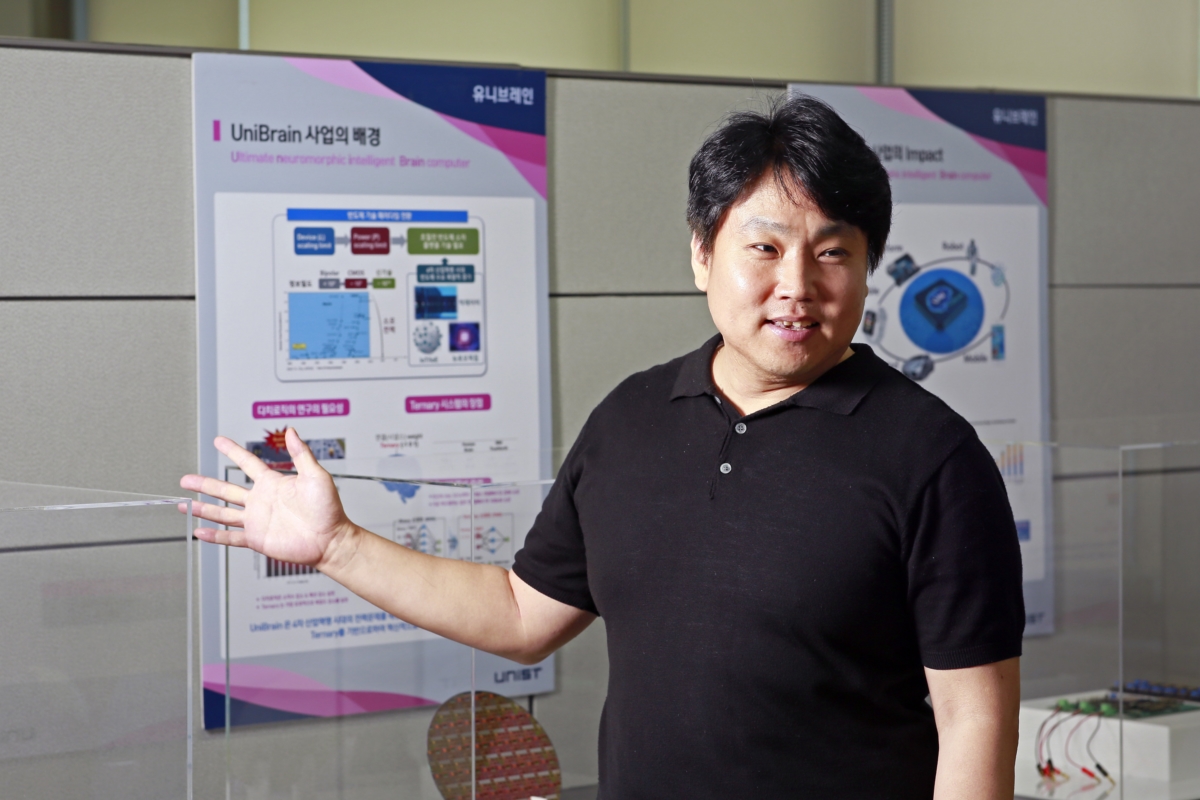

삼성전자에 따르면 김경록 UNIST(울산과학기술원) 전기전자컴퓨터공학부 교수 연구팀은 초절전 `3진법 금속-산화막-반도체`를 대면적 실리콘 웨이퍼에서 구현하는데 성공했다.

이 연구 결과는 지난 15일(영국 현지시간) 세계적인 학술지 `네이처 일렉트로닉스`에 발표됐다.

반도체 업계는 AI, 자율주행, 사물인터넷 등 대규모 정보를 빠르게 처리하는 고성능 반도체를 만들기 위해 반도체 소자 크기를 줄여 집적도를 높였다.

또 현재 2진법 기반의 반도체에서 정보를 처리하는 시간을 단축하고, 성능을 높일수록 증가하는 소비 전력을 줄이는 문제를 해결하기 위해 고민했다.

이런 문제를 해결할 방법으로 `3진법 반도체`가 주목받고 있다.

김경록 교수 연구팀이 개발한 3진법 반도체는 0, 1, 2 값으로 정보를 처리한다.

3진법 반도체는 처리할 정보 양이 줄어 계산 속도가 빠르고 소비 전력도 적다.

반도체 칩 소형화에도 강점이 있다.

예컨대 숫자 128을 표현하려면 2진법으로 8개의 비트(2진법 단위)가 필요하지만 3진법으로는 5개의 트리트(3진법 단위)만 있으면 저장할 수 있다.

현재 반도체 소자의 크기를 줄여 단위 면적당 집적도를 높이는 방식은 소자의 소형화로 인한 양자역학적 터널링 현상이 커져 누설전류가 증가한다.

그로 인해 소비전력도 증가하는 문제가 크다.

연구팀은 발상의 전환을 통해 소비전력 급증의 주요 원인 중 하나인 누설 전류를 반도체 소자에서 정보를 처리하는 상태를 구현하는데 활용한다.

누설전류의 양에 따라 정보를 3진법으로 처리하도록 구현했다.

김 교수 연구팀은 이번 연구를 통해 현재 산업계에서 널리 활용되고 있는 반도체 공정에서 3진법 반도체를 구현해 상용화에 대한 기대감도 높였다.

김경록 교수는 "3진법 반도체는 4차 산업혁명 핵심인 AI, 자율주행, 사물인터넷, 바이오칩, 로봇 등 기술발전에 파급 효과가 있을 것이다"고 말했다.

한편 삼성전자는 파운드리 사업부 팹(FAB)에서 미세공정으로 3진법 반도체 구현을 검증 중이다.

삼성전자는 이번 연구를 지난 2017년 9월 삼성미래기술육성사업 지정테마로 선정, 지원해 왔다.

삼성미래기술육성사업은 국가 미래 과학기술 연구 지원을 위해 2013년부터 10년간 1조5,000억원을 지원, 현재 532개 과제에 6,826억원을 집행했다.