삼성전자가 오는 2023년까지 3나노(나노미터·1㎚=10억분의 1m) 게이트 올 어라운드(GAA) 기술을 적용한 반도체를 양산할 가능성이 떨어진다는 대만 매체의 전망이 나왔다.

20일 업계에 따르면 대만 시장조사업체 디지타임즈리서치의 에릭 첸 연구원은 지난 18일(현지시간) 삼성전자의 초미세공정 경쟁력을 분석한 보고서에서 "삼성전자가 2023년까지 3나노 GAA 공정을 대량 생산으로 전환할 가능성이 낮다"고 분석했다.

GAA가 반도체 초미세공정에서 처음 도입되는 과정이라 수율 확보가 어려워 TSMC의 고객사를 빼앗아갈 정도의 물량을 생산해내긴 어렵다는 이유를 들었다. 삼성전자의 GAA 기술력을 확인하려면 2023년 이후에나 가능할 것이란 게 보고서의 골자다.

디지타임즈리서치는 대만 정보기술(IT) 매체 디지타임즈의 산하기관이다. 디지타임즈는 최근 TSMC와 삼성전자의 초미세공정 경쟁력을 10회에 걸쳐 비교·분석한 기획 시리즈에서 "삼성전자가 10년 안에 TSMC를 이길 가능성은 없다"고 평가한 바 있다.

반도체 업계에선 3나노 양산을 시작한다고 해도 수율 안정화까지는 3~4년이 걸릴 것으로 본다. 삼성전자가 이를 얼마나 단축시키느냐가 3나노 공정 경쟁의 관건이다.

삼성전자는 그동안 GAA 기술을 적용한 3나노 공정과 관련해 내년 양산을 목표로 차질없이 개발 중이라고 밝혀왔다. 삼성전자는 지난달 29일 2분기 실적발표 이후 열린 전화회의(컨퍼런스콜)에서 "GAA는 내년 양산될 3나노 1세대, 2023년 양산될 3나노 2세대에 적용될 예정"이라며 "차질없이 공정을 개발 중"이라고 강조했었다. "이미 3나노 GAA 1세대 공정의 경우 고객사가 제품을 설계하고 있다"고도 했다.

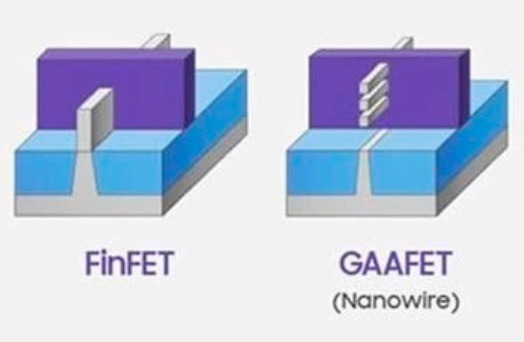

GAA는 기존보다 전류 흐름을 세밀하게 제어할 수 있는 차세대 트랜지스터 구조다. 반도체의 구성을 이루는 트랜지스터는 전류가 흐르는 채널과 채널을 제어하는 게이트로 구분되는데, GAA는 채널의 4면을 게이트가 둘러싸고 있다. 이로 인해 채널 조정 능력이 높아지는 효과를 볼 수 있다. 게이트와 채널이 3면에서 맞닿아 있는 기존 핀펫(FinFET) 구조보다 GAA가 전력효율을 높일 수 있다는 얘기다.

TSMC와 삼성전자는 3나노 공정 도입에서 다른 접근방식을 택했다. TSMC는 기존에 사용하던 핀펫 공정을, 삼성전자는 새로운 GAA 공정을 택했다. 핀펫의 경우 게이트와 채널이 3면에서 맞닿아 초미세공정에선 다소 불리한 기술로 알려져 있지만, 파운드리 시장점유율에서 앞서고 있는 TSMC는 과감한 도전보다는 좀 더 핀펫 공정을 끌고나가는 쪽을 택한 것으로 풀이된다.

TSMC는 3나노보다 더 나아간 2나노 공정부터 삼성과 같은 GAA를 도입할 것으로 전망된다.

업계에선 삼성전자가 GAA를 적용해 양산에 계획대로 성공한다면 3나노 초미세공정 경쟁에서 TSMC보다 유리한 고지에 오를 수 있다고 내다봤다. 삼성전자가 위험을 감수하고 기존에 쓰지 않던 방식을 택한 이유다.

삼성전자는 최근 고객사들에 3나노 공정의 기술 차이를 어필하는 것으로 알려졌다. 도현우 NH투자증권 연구원은 "현재 파운드리 공정 경쟁력은 TSMC가 삼성전자보다 높지만 5나노에서는 근접한 수준, 3나노부터는 삼성의 경쟁력이 더 높아질 것"이라고 했다.

TSMC는 기존에 쓰던 핀펫을 적용하기 때문에 예정대로 내년 7월이면 3나노 칩 양산에 성공할 것이란 게 업계의 관측이다. TSMC는 최근 대만 타이난에 있는 '팹18' 공장에 3나노 공정 장비를 설치한 것으로 알려졌다.

시장조사업체 트렌드포스에 따르면 올 1분기 파운드리 시장에서 TSMC는 55%의 점유율로 1위를 달렸다. 삼성전자는 17%로 TSMC에 이어 2위에 올랐다.

노정동 한경닷컴 기자 dong2@hankyung.com