반도체를 전자기기에 붙일 수 있는 상태로 가공하는 ‘최첨단 패키징’ 경쟁이 거세지고 있다. 불씨를 지핀 것은 미국 정부다. 미 상무부는 지난달 공개한 반도체지원법 가이드라인을 통해 “전공정(칩 생산)을 잘해봤자 패키징을 못 하면 반도체 경쟁력을 회복할 수 없다”며 “시스템 반도체와 메모리의 최첨단 패키징에서 세계적인 기술 선도국이 되겠다”고 선언했다.

○패키징 중요성 더 커진다

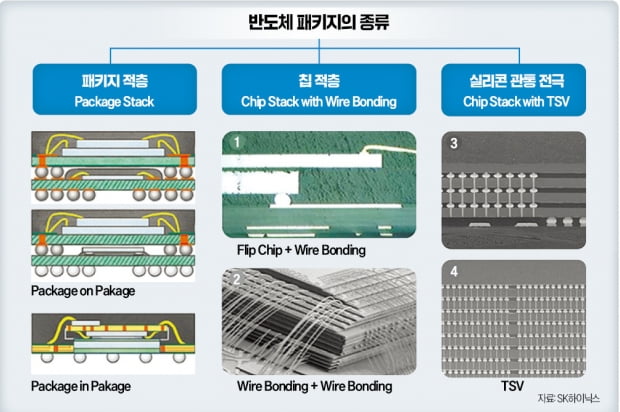

반도체 생산은 크게 △설계 △생산 △패키징 등으로 나뉜다. 설계와 생산을 전(前)공정, 패키징을 후(後)공정이라고 부른다. 반도체 패키징은 반도체를 전자기기에 맞는 형태로 제작하는 공정이다. 칩을 기판 등에 장착하는 과정에서 칩이 외부와 통신할 수 있도록 전기 신호가 흐르는 길을 만들고, 외형도 가공한다.

그동안 반도체 패키징은 전공정에 비해 주목도가 낮았다. 전공정에서 나노미터(㎚·10억분의 1m)와 수율(결함 없는 합격품 비율) 등 첨단 기술 경쟁이 벌어졌다. 분위기가 달라진 것은 글로벌 반도체 업체 간 미세공정 경쟁이 막대한 비용과 기술적 난제라는 한계에 부닥치면서다.

고성능 반도체에 대한 수요를 패키징 기술 혁신으로 극복하려는 움직임이 본격화된 것이다. 여러 종류의 반도체 칩을 효율적으로 담는 것만으로도 공정 미세화 못지않은 효과를 누릴 수 있다는 설명이다. 구글, 애플 등 독자 칩을 개발하는 글로벌 정보기술(IT) 업체가 늘어난 것도 패키징 시장이 뜨겁게 달아오른 배경으로 꼽힌다. 이런 업체들은 자체적인 표준에 따라 패키징을 해 달라고 요구하고 있다. 업계 관계자는 “인공지능(AI), 5G(5세대), 전장 등 다양한 분야에서 고성능·저전력 특성을 갖춘 반도체 패키지 기술도 요구되고 있다”고 설명했다.

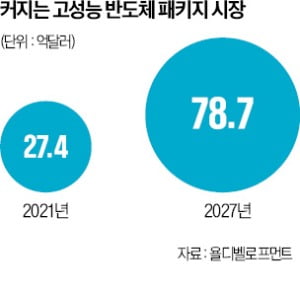

고성능 반도체에 대한 수요를 패키징 기술 혁신으로 극복하려는 움직임이 본격화된 것이다. 여러 종류의 반도체 칩을 효율적으로 담는 것만으로도 공정 미세화 못지않은 효과를 누릴 수 있다는 설명이다. 구글, 애플 등 독자 칩을 개발하는 글로벌 정보기술(IT) 업체가 늘어난 것도 패키징 시장이 뜨겁게 달아오른 배경으로 꼽힌다. 이런 업체들은 자체적인 표준에 따라 패키징을 해 달라고 요구하고 있다. 업계 관계자는 “인공지능(AI), 5G(5세대), 전장 등 다양한 분야에서 고성능·저전력 특성을 갖춘 반도체 패키지 기술도 요구되고 있다”고 설명했다.시장조사 업체 욜디벨로프먼트에 따르면 고성능 반도체 패키징 시장 규모는 2021년 27억4000만달러에서 2027년 78억7000만달러로 확대될 전망이다.

○수직 적층 방식 선호해

패키징은 하나의 패키지에 여러 개의 반도체를 쌓는 ‘수직 적층’ 방식이 있고, 수평으로 붙여넣는 방식이 있다. 수평으로 넣으면 패키지 크기가 커지기 때문에 수직 적층에 대한 선호도가 높다. 수직으로 반도체를 쌓을수록 용량이 늘어나고 전기적 신호 전달 경로가 짧아진다. 건축에서 용적률이 높을수록 고층 건물을 지을 수 있는 것과 비슷한 원리다.이때 패키지 자체의 두께가 늘어나선 안 된다. 반도체 두께를 얇게 만들다 보면 생산 난도가 높아진다. 얇을수록 생산 과정에서 반도체가 물리적 충격에 약해지기 때문이다.

반도체 제품은 패키징을 거쳐야 설계가 잘 됐는지, 공정이 잘 진행됐는지 확인하고 신뢰성 시험 등을 할 수 있다. 원하는 특성 및 신뢰성 기준을 만족하면 개발이 완료된다.

반도체 패키징의 핵심 역할은 △기계적 보호 △전기적 연결 △기계적 연결 △열 방출 등 네 가지로 꼽힌다. 반도체 칩·소자를 EMC와 같은 패키지 재료로 감싸 외부의 기계적 및 화학적 충격으로부터 보호하는 역할이 대표적이다. 반도체 칩의 기본 재료는 실리콘이어서 쉽게 깨질 수 있다. 웨이퍼 공정으로 형성된 구조체들은 기계적, 화학적 충격에도 취약하다. 패키지 재료로 칩을 보호하는 것은 필수다.

물리적·전기적으로 칩을 시스템에 연결하는 역할도 중요하다. 전기적으로는 칩과 시스템을 연결해 칩에 전원을 공급하고, 원하는 기능을 할 수 있도록 신호를 입력하거나 출력할 수 있는 통로를 만들어야 한다. 기계적으로는 칩이 사용되는 동안 시스템에 잘 부착되도록 잘 연결해야 한다. 칩·소자에서 발생하는 열을 빠르게 발산시키는 역할도 한다. 칩이 과열되고 내부 트랜지스터의 온도가 동작 가능 온도 이상으로 올라가면 트랜지스터 동작이 멈출 수 있다.

'절대 강자' 없는 세계 패키징 시장…삼성전자·SK하이닉스, 공격적 투자

이재용 삼성전자 회장은 지난 17일 삼성전자 천안·온양 반도체 패키징 사업 현장을 방문해 “어려운 상황이지만 인재 양성과 미래 기술 투자에 조금도 흔들림이 있어서는 안 된다”고 말했다. 반도체 패키징 분야 인력을 확보하고 신기술을 개발하면서 ‘반도체 초격차’를 이어가겠다는 전략이다.

업계에선 올해 삼성전자가 반도체 패키지에 대해 공격적으로 투자할 것이라는 관측이 나온다. 이 회장이 차세대 패키징 경쟁력 및 연구개발(R&D) 역량에 대해 많은 관심을 보이고 있어서다. 삼성전자는 지난해 말 조직개편을 통해 DS(반도체) 부문 내 패키징 사업 전담 조직인 AVP(어드밴스트 패키지)팀을 신설했다. 최근엔 TSMC 반도체 패키징 분야 전문가인 린준청 씨를 부사장으로 영입했다. 린 부사장은 AVP팀에서 첨단 패키징 기술 개발 업무를 맡는다.

SK하이닉스도 첨단 반도체 패키징의 중요성을 인식하고 투자하고 있다. SK하이닉스는 미국에 150억달러를 투자해 첨단 패키징과 R&D센터를 건설한다. 최태원 SK그룹 회장은 지난해 조 바이든 미국 대통령과 백악관 화상 면담에서 이 같은 내용의 투자 계획을 밝혔다.

업계 관계자는 “첨단 패키징 역량이 반도체 사업 핵심 경쟁력으로 부상했다”며 “미 상무부가 공개적으로 ‘패키징 허브’를 육성하겠다고 나선 것은 예삿일이 아니다”고 말했다. 미 상무부는 지난달 말 “미국 땅에 다수의 최첨단 패키징 시설이 들어서도록 정부가 10년간 지원할 것”이라고 설명했다.

미국 인텔과 대만 TSMC도 일찌감치 첨단 패키징에 적극 투자하고 있다. 시장조사업체 욜디벨롭먼트에 따르면 지난해 세계 첨단 패키징 시장 설비투자 규모 중 59%를 인텔과 TSMC가 가져갔다. TSMC는 지난해 11월 첨단 패키징 생태계인 ‘3D(3차원) 패브릭 얼라이언스’도 조직했다. 자체 패키징 기술을 표준화하면서 시장 주도권을 빠르게 확보하겠다는 취지로 풀이된다.

업계에 따르면 아직 글로벌 반도체 패키징 시장의 ‘절대 강자’는 없다. 반도체 생산 분야에서 파운드리(반도체 위탁생산)는 TSMC가 점유율 58.5%로, 메모리반도체(D램)는 삼성전자가 45.1%로 압도적 1위인 것과 다르다. 패키징 시장 점유율 1위는 대만 ASE가 30%, 2위는 미국 앰코가 15%다. 절대 강자를 목표로 한 경쟁이 올해를 기점으로 더 치열해질 전망이다.

정지은 기자 jeong@hankyung.com